La Compuerta NOT RTL

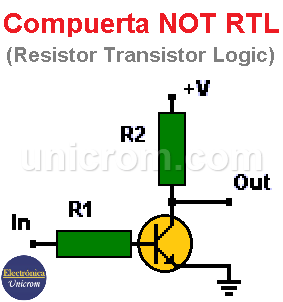

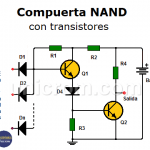

Para entender mejor la Compuerta NOT RTL, se recomienda leer primero el tutorial: Niveles Lógicos. La forma más sencilla de obtener una compuerta NOT o inversora con tecnología RTL es con el circuito siguiente.

Es fácil ver que:

- Cuando en la entrada (In) hay un “0” lógico, el transistor no conduce (está en corte), no hay corriente por R2 y en la salida (Out) hay un “1” lógico.

- Cuando en la entrada (In) hay un “1” lógico, el transistor conduce (está en saturación) y el voltaje colector – emisor es de aproximadamente 0,3 voltios y en la salida (Out) hay un “0” lógico.

Este tipo de tecnología: Resistor Transistor Logic es relativamente antigua y tiene una serie de limitaciones. Entre ellas están:

- La resistencia de entrada tiene un valor de 470 ohmios (resistencia R1 en la base del transistor).

- La resistencia de salida es de 640 Ohmios (resistencia R2 en el colector del transistor).

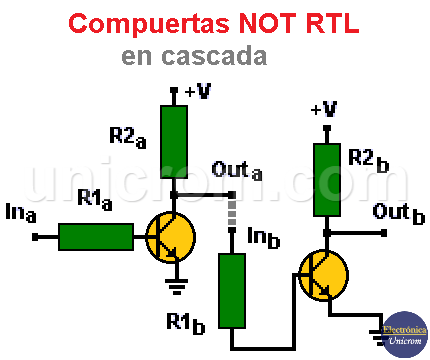

Compuertas NOT RTL en cascada

Se asume que este tipo de compuertas se interconectan entre ellas, siendo natural que una salida de una compuerta RTL se conecte a una entrada de una compuerta RTL. Siendo este el caso, es normal que la corriente que ingresa por la base del transistor, pase por la resistencia de 640 y la de 470 ohmios. Ver gráfico inferior.

Cuando en la entrada Ina hay un “0” lógico, el transistor está en corte. Esto hace que las resistencias R2a y R1b estén en serie. La corriente a través de estas resistencias es la corriente de base del segundo transistor y se obtiene utilizando la ley de Ohm Ib = (+V – Vbe) / (R2a + R1b).

Reemplazando los valores: Ib = (3,6 – 0,7) / (640 + 470) = 2.612 mA, donde:

En este caso el primer transistor está en corte (no conduce) y la corriente que pasa por la resistencia de que está conectada a la entrada del segundo transistor, pasa por la resistencia conectada al colector del primer transistor (ver gráfico anterior), donde:

- V+ = “1” lógico = 3.6 V.

- 0.7 voltios = voltaje base emisor de un transistor en conducción.

- R1 = 470 ohmios = resistencia conectada a la base

- R2 = 640 ohmios = resistencia conectada al colector

Con esta corriente y una ganancia del transistor aproximada de 30, se logra su saturación sin problemas. Se logra de esta manera obtener a la salida un “0” lógico después de invertir la señal de entrada (“0” lógico) dos veces. *