Compuertas NOR y NAND RTL (Resistor Transistor Logic)

Las compuertas NOR y NAND RTL usan la tecnología Resistor Transistor Logic que es relativamente antigua y tiene una serie de limitaciones.

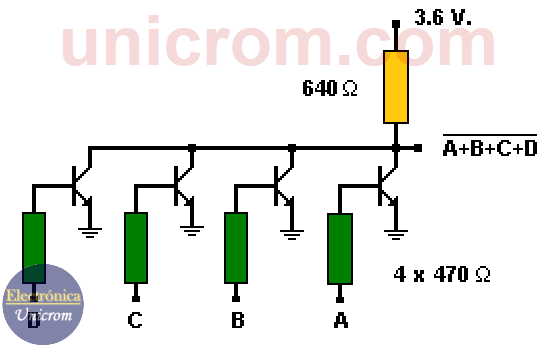

Compuerta NOR con tecnología RTL

Si se desea implementar una compuerta NOR con tecnología RTL, el diagrama sería como se muestra en la primera imagen. En este caso cada entrada tiene una resistencia de 470 ohmios y un transistor.

Al final todos los colectores de los transistores se conectan en punto común y comparten una sola resistencia de 640 ohmios que se conecta a 3,6 voltios.

Si se desea obtener una compuerta OR, se colocaría a la salida de esta compuerta un inversor (una compuerta NOT con tecnología RTL) como el que se muestra en el primer diagrama del tutorial Compuerta NOT con tecnología RTL.

Si cualquiera de las entradas A, B, C o D se pone en “1” lógico, el transistor correspondiente se satura y hace que en la salida haya un “0” lógico. La salida sólo estará en ‘1″ lógico cuando todas las entradas A, B, C, D estén en “0” lógico.

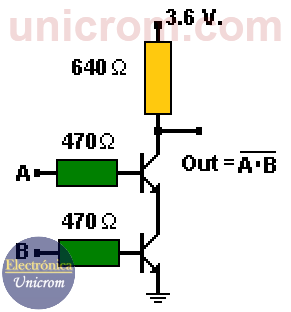

Compuerta NAND con tecnología RTL

La compuerta NAND con tecnología RTL se implementa con una resistencia y un transistor para cada una de las entradas de la compuerta, como se muestra en la figura.

En este caso, tomando en cuenta que el voltaje colector – emisor de un transistor saturado es de aproximadamente 0.3 voltios, el voltaje de salida en nivel bajo sería de 0.6 voltios.

Hay que recordar que si este nivel de voltaje (0.6 voltios) va a servir de entrada a otro circuito RTL, faltaría muy poco para que esta señal (“0” lógico) haga conducir el transistor de entrada (0.7 voltios en la unión base-emisor) de la siguiente compuerta, interpretándose erróneamente esta entrada como un “1” lógico.

La situación anterior se presenta con una compuerta de 2 entradas. Si se implementara una compuerta con 3 entradas, la salida “0” lógico sería de 0.9 voltios y no se podría interpretar como nivel bajo por la compuerta que sigue (problema, pues pondría en conducción el transistor cuando no debería hacerlo).

Este es uno de los problemas con las compuertas RTL y se hace más notorio con el aumento de la frecuencia de operación.

Otra opción sería utilizar las compuertas NOR y NOT y el teorema DeMorgan para implementar una compuerta AND y NAND. *

Las Compuertas NOR y NAND RTL están prácticamente en desuso, pero se pueden seguir implementando en casos sencillos.