La compuerta NOR

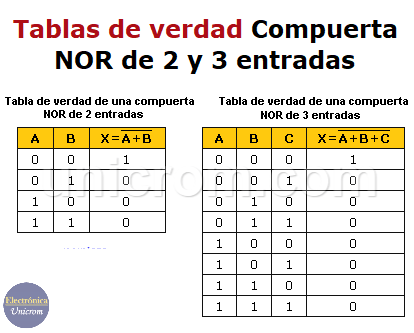

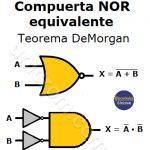

La compuerta NOR o compuerta NO O es una compuerta lógica que entrega en su salida un “0” lógico en todas las posibles combinaciones de sus entradas, menos cuando estas están todas en “0” lógico, en este caso la salida es un “1” lógico. Ver las tablas de verdad en diagramas inferiores.

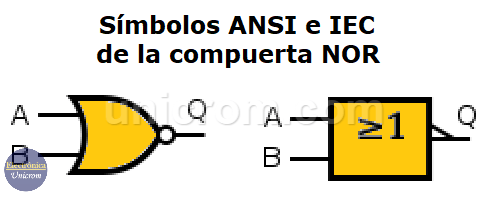

Hay dos símbolos aceptados para esta compuerta. Uno del estándar Americano (ANSI) y otro del estándar Europeo (IEC).

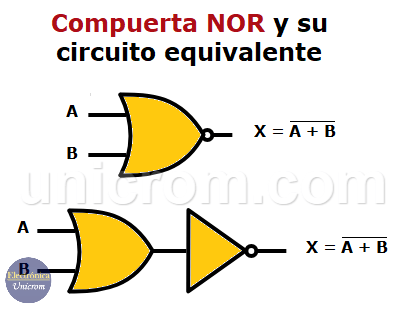

Una compuerta NOR se puede implementar con la concatenación de una compuerta OR con una compuerta NOT, como se muestra en la siguiente figura.

Del gráfico anterior se ve que la salida de la compuerta OR es A + B. Esta salida se pasa por el inversor o compuerta NOT y se obtiene: X = A + B.

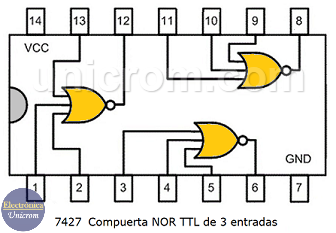

Al igual que en el caso de la compuerta OR, esta compuerta se puede encontrar en versiones de 2, 3 o más entradas.

- En la versión TTL están: 7402 (2 entradas), 7427 (3 entradas), etc.

- En la versión CMOS están: 4001 (2 entradas), 4025 (3 entradas), etc.

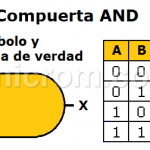

Las tablas de verdad de estas dos tipos de compuertas son las siguientes:

Como se puede ver la salida X solo es “1”, cuando todas las entradas son “0”.

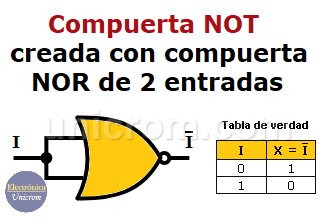

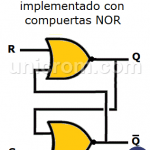

¿Cómo crear una compuerta NOT?

Un caso interesante de la compuerta NOR, al igual que la compuerta lógica NAND, es cuando las entradas A y B ó A, B y C (en el caso de una compuerta de 3 entradas) se unen, para formar una sola entrada. (Ver las tablas de verdad anteriores). En este caso la salida (X) tiene exactamente el valor opuesto a la entrada.

Ver la primera y la última fila de las tablas de verdad anteriores. En otras palabras: Con una compuerta No O se puede lograr el comportamiento de una compuerta NOT.

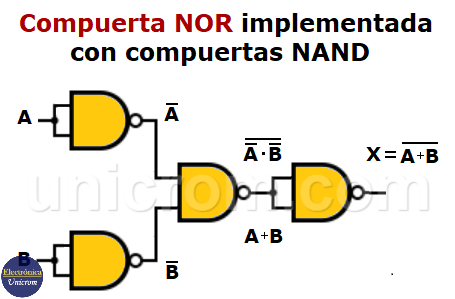

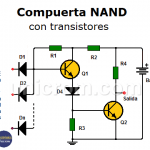

¿Cómo crear una compuerta NO o con compuertas NAND?

Es posible crear una compuerta NOR usando compuertas NAND. Observando el siguiente diagrama se ve que las entradas A y B se invierten después de pasar por las primeras dos compuertas NAND obteniendo A’ y B’.

Estas dos salidas sirven de entradas para la tercera compuerta NAND, obteniéndose a su salida (A’·B’)’. La salida (A’·B’)’ es equivalente a A+B (teorema de Morgan). Esta última salida es aplicada finalmente a la última compuerta NAND y para obtener la salida final X = (A+B)’. La misma salida de una compuerta NOR normal.

X = A + B = (A+B)’

A continuación se presenta la distribución interna del circuito integrado TTL 7427 que tiene 3 compuertas NOR de 3 entradas. Estas compuertas tienen la tabla de verdad de 3 entradas que se muestra en un gráfico anterior.