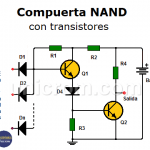

Funcionamiento de una compuerta NAND TTL

Salida en estado bajo (0 lógico) de NAND TTL

Q1 funciona en activa inversa (unión B-C 0n, unión B-E Off). Q2 y Q3 funcionan en saturación. Q4 está cortado, debido a la presencia de D1. Vsal = Vce(sat) = 0.2v = Vol.

Salida en estado alto (1 lógico) de NAND TTL

Al menos una entrada está a nivel bajo. La unión B-E de Q1 conduce, por lo que la tensión de base de Q1 es de 0.2 + 0.7 = 0.9V, lo que es insuficiente para que Q2, Q3 y el diodo B-C de Q1 conduzcan.

Por lo tanto Q2 y Q3 quedan cortados. Y la tensión de salida Vs es aproximada a:

Otras puertas TTL

Por: Liliana Sosa liliy_sosa@hotmail.com

Dig_Tecnologia_TTL6.asp