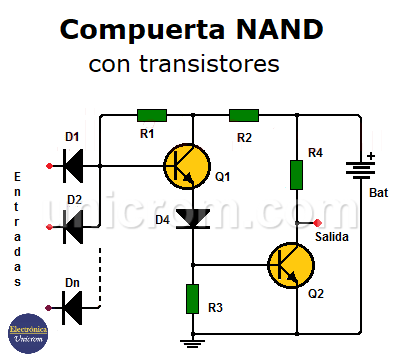

Compuerta NAND con transistores

Este circuito compuerta NAND con transistores, simula el funcionamiento de una compuerta NAND de dos o más entradas, utilizando transistores bipolares y un diodo por cada entrada: D1, D2, … Dn.

Este método se puede utilizar cuando sea necesario realizar esta operación lógica “Y” y estemos usando solo transistores o el diseño no amerite usar una compuerta lógica típica CMOS o TTL.

Funcionamiento de la compuerta NAND con transistores

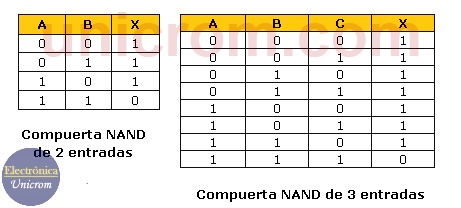

En la tabla de verdad que se muestra más abajo se muestra el comportamiento de una compuerta NAND, y se observa que la salida estará en nivel lógico “0” cuando todas las entradas tengan un nivel lógico “1”.

Cualquier otra combinación de entradas (“0” y “1”) causará que la salida tenga un nivel lógico “1”.

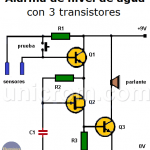

Del diagrama se puede observar que el circuito utiliza dos transistores que trabajan en corte (no conduce corriente) o en saturación (conduce corriente).

Tablas de verdad de una compuerta NAND de 2 y 3 entradas

Tomando el caso de la primera tabla de verdad (tiene 2 entradas). Si las dos entradas son “1”, los dos diodos no conducirían, pues están polarizados en inverso. El transistor Q1 se polariza a través de la resistencia R1 y entra en saturación. La corriente de saturación de del transistor Q1 polariza Q2 y lo satura, causando que en la salida, que está en el colector de Q2, aparezca un nivel lógico “0”.

Si cualquiera o todas las entradas tienen un nivel lógico “0”, la base del transistor no tiene voltaje suficiente para polarizar el transistor Q1 y este no conduce. Sin la corriente de colector de Q1, no se polariza Q2, este no conduce y la salida tendrá un nivel lógico “1”.

Nota: El circuito se alimenta con 5 voltios.

Lista de componentes del circuito

- 2 transistores NPN 2N2222 o equivalente (Q1, Q2)

- “n” diodos semiconductores 1N914 o equivalente (D1, D2, D3, … Dn)

- 1 resistencia de 2.2 K (R1)

- 1 resistencia de 470 ohmios (R2)

- 1 resistencia de 47 K (R3)

- 1 resistencia de 2.7 K (R4)